### Latency Interfaces for Systems Code

Présentée le 8 septembre 2023

Faculté informatique et communications Laboratoire des systemes fiables Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

#### Rishabh Ramesh IYER

Acceptée sur proposition du jury

Prof. E. Bugnion, président du jury

Prof. G. Candea, Prof. A. Argyraki, directeurs de thèse

Prof. J. Hoffman, rapporteur

Prof. M. Swift, rapporteur

Dr J. Mogul, rapporteur

Prof. T. Bourgeat, rapporteur

While today's world is one of immediacy, life's greatest goals still do not materialize overnight. Rather, they materialize through resilience, perseverance and the lessons of failure.

— Rafael Nadal

To my family...

## Acknowledgements

I look back upon the last six years fondly. While there were many challenges and several ups and downs, I found great friends and inspiring mentors who have celebrated my victories and helped me persevere through the bad times. While this thesis—out of necessity—lists only my name, it would not have existed without these amazing people, many of whom I list below.

My advisors, George Candea and Katerina Argyraki: George and Katerina have had an indelible impact on not only this thesis but also on my approach to research. George has instilled in me the importance of thinking big and focusing on research that will endure the test of time (your paper should be relevant in 100 years!), while simultaneously emphasizing the importance of being meticulous and getting every minuscule detail right (what will your grandchildren think of you if they discover a typo in your work?). Throughout my Ph.D, George set uncompromising standards and pushed me to improve as a researcher every single day, but constantly led by example and demonstrated that those standards could indeed be met.

Katerina, whom I consider a master of simplicity, has taught me the ability to distill and precisely communicate the key ideas underlying a research project. She often had to do this the hard way, by carefully unraveling the core ideas from my tangled thoughts, but remained patient with me throughout, which is something I will always be thankful for. Katerina's ability to focus on what matters goes beyond research; I have often found myself in her office, venting about either paper rejections or why my research is pointless, but she always managed to miraculously tell me precisely what I needed to hear in order to soldier on.

Both George and Katerina have gone well beyond what is typically expected of an advisor in terms of looking out for me, both personally and professionally. In particular, both of them had unwavering faith in me and the topic of my thesis, even when I had lost faith in both. I sincerely hope that the end of graduate school does not mean the end of having them as advisors, since I plan to rely on their advice for the foreseeable future. Thank you, George and Katerina, for everything. This thesis belongs to the two of you as much as it does to me.

My thesis committee and mentors at EPFL: I am grateful to Jan Hoffman, Mike Swift, Jeff Mogul, Thomas Bourgeat, and Ed Bugnion for serving on my thesis committee. Jeff and Thomas in particular, read the entire document in great detail and provided feedback that significantly improved the thesis. Ed, apart from being an amazing committee president, has been a great mentor over the past few years and has always taken the time to provide valuable feedback on my research ideas.

I would also like to thank three other professors at EPFL: Babak Falsafi, James Larus, and Sanidhya Kashyap. Babak hired me as an intern at EPFL when I was still an undergrad at IIT Bombay. This was my first foray into research and without this opportunity (and his subsequent letter of recommendation), I would never have pursued a Ph.D. Jim, like Ed, always made time to give me feedback on my research ideas. What I particularly appreciated about Jim was his brutally honest feedback, which often laid bare flaws that I had hoped others would ignore. Finally, Sanidhya (whom I first met outside as a fellow student at a conference), has been halfway

between a friend and a mentor and someone who has always made time for me.

**DSLAB:** Next, I would like to thank my fellow members of the Dependable System Lab (DSLAB), which has been my home for the last six years.

Arseniy Zaostrovnykh was my first friend in the lab and remains one of my closest friends to this day. Apart from being one of the sharpest people I know and an invaluable sounding board for anything verification-related, Arseniy has been the one person who not only put up with but also shared my craziness and lack of self-preservation when it came to sporting activities. Arseniy and I have spent countless hours together biking, rafting, climbing, competing in the gym, axe-throwing, and even wrestling all over the office floor. This has led to some incredibly memorable incidents that I would not trade for all the world: from jumping into Lake Geneva together after an 8-hour bike ride circumnavigating it, to me tearing a shoulder ligament when racing down a ski slope and having to take a 12-hour flight to Canada while being unable to move my neck after a particularly intense wrestling match with Arseniy.

Solal Pirelli and I joined the Ph.D program at the same time and have been through many of the ups and downs of a Ph.D in DSLAB together. Solal is one of the most unique people I have met and talking to him always provides a perspective that I will not get from anyone else. This unique perspective has also significantly contributed to this thesis; it was a stray comment by Solal that actually provided an escape from one of the deepest ruts I found myself in during the Ph.D and provided the spark for what turned into Chapter 4 of this thesis.

Lei, Can, Yugesh, and Jiacheng represent the new generation of DSLAB. While our Ph.Ds did not overlap for as long as I would have liked, I am grateful to them for breathing new life into DSLAB, particularly after Arseniy had left. I will particularly cherish my incredibly competitive board game battles with Can, be it while playing Carcassonne, Avalon, Cascadia, or Citadels, and my multi-hour discussions with Yugesh on history, spirituality, and religion. I am also grateful to Jaicheng for expanding upon my thesis work in a way that I never could have done myself.

I would also like to thank the interns I have worked with over the past 6 years—Musa, Daneshvar, Yugesh, Vlad, Ayoub, Beyazit, and Mihai—many of whom made small, but critical contributions to the work presented in the thesis. Musa, in particular, played a pivotal role in getting Concord (Chapter 3) off the ground, while Ayoub was responsible for extending my ideas to cryptographic code (§6.4.2). What has been a particular source of pride is that nearly all of my past interns are now successful Ph.D students in great graduate programs around the world.

Finally, I am incredibly grateful to our lab admin Celine Brzak, and her three canine assistants Beary, River, and Soho. Celine is not only the best possible lab admin—who ensured that I never had to worry about dealing with any EPFL bureaucracy—but also an endless source of positivity. It is virtually impossible to leave Celine's office without a big smile on one's face and Celine, Beary, River, and Soho were usually the ones who managed to cheer me up even when I was having the worst of days.

**NAL:** I would also like to thank my fellow members of the Network Architecture Lab (NAL), Luis, Pavlos, Mia, Zeinab, and Catalina.

Luis Pedrosa was a postdoc in NAL when I began my Ph.D and the primary collaborator on the first two papers I submitted as a Ph.D student. Luis and I spent most of the summer of 2018 in front of a whiteboard—he lost an entire summer's worth of time, while I gained an understanding of compilers, program analysis, and network functions. I will always be grateful to Luis for being so generous with his time and for helping me find my footing in a field of research that was vastly different from what I studied as an undergrad.

I am grateful to Pavlos for his sagacious advice on how to navigate the trials and tribulations of a Ph.D, Mia for introducing me to the sport of spikeball, and Zeinab and Catalina for our incredibly interesting lunch and dinner conversations that revolved around the peculiarities of India, Lebanon, and Chile, respectively.

Sylvia Ratnasamy, Scott Shenker and the Netsys Lab at UC Berkeley: I am grateful to Sylvia and Scott for hosting me at Berkeley for 6 months of my Ph.D. Both Sylvia and Scott are researchers whose work I have admired for the longest time, and being able to collaborate with the two of them was among the highlights of my Ph.D. I am also grateful to the members of 419 Soda: Narek, Vivian, Tenzin (honorary member), Wen, and Akshay who were incredibly welcoming and helped me settle in at Netsys remarkably quickly.

**Siddharth Gupta and Pakshal Bohra:** Sid and Pakshal have been my two closest friends during my Ph.D, they are the ones who know me best and the ones I rely on above everyone else during my worst days.

Sid (who is often been referred to as my work-wife) and I have navigated nearly every up and down in the Ph.D together. Over the past six years, Sid was not only a constant source of inspiration with his uniquely creative approach to research but also my companion on hundreds of walks along the shores of Lake Geneva where we discussed work, life, and everything in between, my ski buddy, my fellow gourmet, the one who effectively filed my tax returns (since I simply copy-pasted what he painstakingly filed and changed the name), and the one who frequently rescued me from both embarrassing and life-threatening situations. It is proving surprisingly difficult for me to summarize Sid's role over the past 6 years in just a few lines, so I will instead say this: I hope everyone finds a friend like Sid to share their Ph.D experience with, it is among the best things that can happen to you.

Pakshal has been one of my closest friends since we first shared a dorm together back at IIT Bombay over 10 years ago. While we initially bonded over our shared love for Man Utd and Nadal, I have come to rely on Pakshal to tell me the things I do not like to admit to myself. Pakshal is incredibly patient and has put up with several of my idiosyncracies over the past 10 years; from the times when I would make him walk several kilometers out of the way at IIT so that I could catch my favorite Pokemon in Pokemon Go, to my insistence that we always walk back after eating out at a restaurant no matter how long the walk may be. As I prepare to leave Switzerland (while Pakshal plans to stay on), one of the things I am most sad about is the fact that my streak of playing hundreds of games with Pakshal on every single version of FIFA since 2013 will finally come to an end.

Mario Drumond and Marios Kogias: Mario and Marios have been akin to two older brothers

throughout my Ph.D journey.

Mario was my supervisor when I was an intern at EPFL more than 7 years ago, and while he failed to show up and left me hanging on my very first day (he was too drunk from the night before :P), it was primarily due to him, and how much he seemed to be enjoying his Ph.D, that I chose to pursue a Ph.D myself. Mario is one of the most entertaining people I have met; there is never a dull moment when he is around and my Ph.D journey would have been much less enjoyable without him constantly mocking my all-too-frequent bouts of negativity, my obsession with elegant research, and my need to pursue unnecessary "feats of strength". That said, Mario has also been a constant source of support and guidance and is one of the most large-hearted people I have ever met, always being the first to celebrate my victories.

Marios is the best systems Ph.D student I have ever met and (outside of George and Katerina) has contributed the most to both the technical content of this thesis and my growth as a systems researcher. He is always the first person I go to whenever I need feedback on a new research idea and I will always cherish the hundreds of hours we spent discussing random research ideas. What I find particularly heartwarming is that our relationship seems to have been symbiotic: while Marios started out working exclusively on low-latency datacenter systems, and I was more focused on program analysis and hardware, Marios has now begun publishing in conferences focused exclusively on programming languages research [152] while my latest publication is targeted at improving the efficiency of low-latency datacenter systems [123]. Marios has also been a great friend outside of work and was not only my first driving instructor, but also the one who taught me to vacation as the Greeks (apparently) do, which involves doing nothing other than swimming, sleeping, eating, and lazing on the beach.

**Sahand Kashani and Mahyar Emami:** I am also grateful to my fellow members of FUBAR, Sahand, and Mahyar, for being two of the most dependable friends that one could ever ask for.

Sahand, in particular, exemplifies the qualities of discipline and perseverance; if I had to pick one person in the world to complete an assigned task in the allotted time, I would pick Sahand in a heartbeat. Sahand's discipline and perseverance have been an inspiration throughout my Ph.D and I will be glad if I am able to inculcate even a small fraction of his qualities. Outside of work, Sahand has also been just as enthusiastic as Arseniy when it comes to sporting activities and has been a frequent companion on long bike rides, hikes, and bouldering workouts but only if we agreed to pursue said activity either indoors or before sunrise, given his pathological fear of being sunburnt. He has also been our resident evangelist for Italian food, with his insistence on visiting an Italian restaurant at least once a week.

Mahyar is a man of few words, but when he speaks he is always worth listening to. Mahyar possesses a keen understanding of people and has often given me invaluable advice on how to deal with tumultuous situations. TU, Sahand and Mahyar for always keeping the door to your office open for me.

**Other friends at EPFL and in Lausanne:** There are several others at EPFL whom I have been fortunate enough to call friends and who have greatly enriched my Ph.D journey. I am grateful to Venu for all the cricket games and bouldering sessions, and Aditya for the football games,

constant banter, being my fellow chess fanatic, and introducing me to Brandon Sanderson. I am also grateful to Arash for teaching me how to enjoy the little things in life, Adrien for providing a unique mixture of craziness and empathy, Mark for always being encouraging, and Oggy, Negar and Tesca for our fun dinners together.

I am also thankful to the members of Lausanne's Ultimate Frisbee Pickup social team, in particular Lee Sze Chuin, Marc Checkly, and Enrico Eberhard. Our biweekly frisbee games were something I actively looked forward to, and provided a welcome respite from all things EPFL.

There are almost certainly several other friends whom I have missed; please know that this was done inadvertently and that all of you played a huge role in making my PhD journey worthwhile.

**Family:** Finally, I am eternally grateful to my parents and my sister Rithvika for their unconditional love and support throughout the past six years. Trying to find the right words to thank them is a futile endeavor. Amma, Appa, and Rithu, you know how much you mean to me. This thesis is dedicated to the three of you.

Lausanne, August 31, 2023

Rishabh Iyer

### **Abstract**

This thesis demonstrates that it is feasible for systems code to expose a latency interface that describes its latency and related side effects for all inputs, just like the code's semantic interface describes its functionality and related side effects.

Semantic interfaces, such as code documentation, header files, and specifications, are indispensable. By providing a succinct summary of a system's functionality, they make it possible for developers to efficiently reason about, use and deploy code they did not write themselves. In contrast, there is no equivalent construct that describes latency behavior in a way that is simultaneously succinct, precise, and complete. Widely-used representations such as envelopes (e.g., probabilistic upper bounds or asymptotic time complexity) or benchmarks (e.g., SPEC or TPC-C results) provide an incomplete understanding of latency, leading to hiccups and meltdowns in production when the workload or runtime environment changes in unpredicted ways.

We take a three-part approach to realize latency interfaces for systems code.

First, we show how to design datacenter systems that provide predictable latency behavior while sustaining high throughput. We present Concord, an efficient runtime for datacenter applications that demonstrates how the careful approximation (as opposed to canonical implementation) of theoretically optimal scheduling policies enables datacenter systems to sustain significantly higher throughput while continuing to meet the same latency targets.

Second, we propose that the latency interface of a system be a program that accepts the same input(s) as the system and outputs its processing latency. We contribute three key ideas that help summarize latency in a succinct, precise, and complete manner: latency-critical variables, which provide succinct abstractions of how the system interacts with its environment, the latency resolution, which provides readers of the interface with explicit control over the trade-off between succinctness and precision, and deployment-specific interfaces which enable users of the system to reason precisely about its latency behavior in their distinct deployment environments. We concretize this representation in the domain of network functions (NFs) and present LINX, a program analysis tool that automatically extracts latency interfaces from NF implementations. We demonstrate that the LINX-extracted interfaces are succinct, precise, and complete and show how they can be used to identify latency regressions, diagnose and fix performance bugs, as well as identify the latency impact of NIC offloads.

Third, we present CFAR, a technique, and tool that allows developers to reason precisely about micro-architectural side effects (specifically CPU cache usage) of systems code. CFAR introduces memory distillates, an intermediate representation that contains all information relevant to how a program accesses memory and discards everything else. CFAR automatically extracts memory distillates from systems code and allows developers to query the distillate to answer specific questions about the code's cache usage. We demonstrate that CFAR enables developers to not only identify inputs that lead to inefficient cache usage and security vulnerabilities in their own code, but also reason about the performance impact of using third-party code.

### Résumé

Cette thèse démontre qu'il est possible pour le code système d'exposer une interface de latence qui décrit la latence et les effets secondaires associés pour toutes les entrées, tout comme une interface sémantique décrit les fonctionnalités et les effets secondaires.

Les interfaces sémantiques, telles que la documentation, les fichiers d'en-tête et les spécifications, sont indispensables. En fournissant un résumé succinct des fonctionnalités d'un système, elles permettent aux développeurs de raisonner, d'utiliser et de déployer efficacement du code qu'ils n'ont pas écrit eux-mêmes. En revanche, il n'existe pas d'équivalent décrivant la latence de manière succincte, précise et complète. Des représentations largement utilisées telles que les enveloppes (par exemple, limites supérieures probabilistes ou complexité temporelle asymptotique) ou les benchmarks (par exemple, résultats SPEC ou TPC-C) fournissent une description incomplète de la latence, conduisant à des ratés et des effondrements en production lorsque la charge de travail ou l'environnement d'exécution changent de manière imprévue.

Nous adoptons une approche en trois parties pour réaliser des interfaces de latence pour le code système.

Tout d'abord, nous montrons comment concevoir des applications pour centre de données offrant un comportement de latence prévisible tout en maintenant un débit élevé. Nous présentons Concord, un environnement d'exécution efficace pour ces applications, qui démontre comment l'approximation minutieuse (par opposition à l'implémentation exacte) de techniques théoriquement optimales permet de maintenir un débit nettement plus élevé tout en respectant les mêmes objectifs de latence.

Deuxièmement, nous proposons que l'interface de latence d'un système soit un programme qui accepte les mêmes entrées que le système et retourne sa latence. Nous apportons trois idées clés qui aident à résumer la latence de manière succincte, précise et complète : les variables critiques en matière de latence, qui décrivent succinctement la manière dont le système interagit avec son environnement, la résolution de latence, qui fournit aux lecteurs de l'interface un contrôle explicite entre concision et précision, et les interfaces spécifiques au déploiement, qui permettent aux utilisateurs du système de raisonner précisément sur son comportement de latence dans leurs environnements spécifiques. Nous concrétisons cette représentation dans le domaine des fonctions réseau et présentons LINX, un outil d'analyse qui extrait automatiquement les interfaces de latence des implémentations de ces fonctions. Nous démontrons que les interfaces extraites par LINX sont succinctes, précises et complètes et montrons comment elles peuvent être utilisées pour identifier les régressions de latence, diagnostiquer et corriger les bugs de performances, ainsi qu'identifier l'impact sur la latence des fonctionnalités de déchargement.

Troisièmement, nous présentons CFAR, une technique et outil qui permet aux développeurs de raisonner précisément sur les effets secondaires micro-architecturaux (en particulier l'utilisation du cache CPU) du code système. CFAR introduit les distillats de mémoire, une représentation intermédiaire qui contient toutes les informations pertinentes sur la manière dont un programme accède à la mémoire et rien d'autre. CFAR extrait automatiquement les distillats de mémoire depuis du code système, et permet aux développeurs d'utiliser un distillat pour répondre à

#### Résumé

des questions spécifiques sur l'utilisation du cache. Nous démontrons que CFAR permet non seulement aux développeurs d'identifier les entrées qui conduisent à une utilisation inefficace du cache et à des vulnérabilités de sécurité dans leur propre code, mais également de raisonner sur l'impact de l'utilisation de code tiers sur la performance.

# Contents

| A  | cknow                                  | ledgem                                                          | ients                                                                  | j                                             |

|----|----------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------|

| Al | ostrac                                 | et                                                              |                                                                        | vii                                           |

| Li | st of I                                | Figures                                                         |                                                                        | xiv                                           |

| Li | st of T                                | <b>Tables</b>                                                   |                                                                        | <b>xv</b> i                                   |

| Ι  | Sett                                   | ing the                                                         | stage                                                                  | 1                                             |

| 1  | Intr                                   | oductio                                                         | n                                                                      | 3                                             |

|    | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Reason<br>Thesis<br>1.2.1<br>1.2.2<br>1.2.3<br>Thesis<br>Thesis | Ining about System Latency Today                                       | 4<br>5<br>6<br>8<br>9<br>10<br>10<br>11<br>12 |

|    | 1.0                                    | Diono                                                           | grapine notes                                                          |                                               |

| 2  |                                        | kground                                                         |                                                                        | 13                                            |

|    | 2.1                                    | -                                                               | senting System Latency Today                                           | 13                                            |

|    |                                        | 2.1.1 2.1.2                                                     | Asymptotic Bounds on Time Complexity                                   | 13<br>13                                      |

|    |                                        | 2.1.2                                                           | Benchmark Scores                                                       | 13                                            |

|    |                                        | 2.1.3                                                           | Service Level Objectives                                               | 15                                            |

|    |                                        | 2.1.5                                                           | Performance Annotations                                                | 15                                            |

|    |                                        | 2.1.6                                                           | Summary                                                                | 16                                            |

|    | 2.2                                    |                                                                 | ng Latency Properties from Code                                        | 16                                            |

|    |                                        |                                                                 | Traditional Profiling                                                  | 17                                            |

|    |                                        | 2.2.2                                                           | Trend Profiling                                                        | 17                                            |

|    |                                        | 2.2.3                                                           | Discovering Adversarial Workloads                                      | 18                                            |

|    |                                        | 2.2.4                                                           | Verifying Latency Behavior                                             | 20                                            |

|    |                                        | 2.2.5                                                           | Takeways                                                               | 22                                            |

| II | Bu                                     | ilding S                                                        | Systems with Predictable Latency Behavior                              | 23                                            |

| 3  | Mee                                    | ting Mi                                                         | crosecond-Scale, Tail Latency Objectives while Sustaining High Through | 1-<br>25                                      |

### Contents

|    | 3.1                                           | Proble         | em Definition                                                       | 25       |

|----|-----------------------------------------------|----------------|---------------------------------------------------------------------|----------|

|    | 3.2 Throughput Overheads at Microsecond-Scale |                |                                                                     |          |

|    |                                               | 3.2.1          | System Model                                                        | 27       |

|    |                                               | 3.2.2          | Sources of Throughput Overhead                                      | 28       |

|    | 3.3                                           | Efficie        | ent Microsecond-Scale Scheduling                                    | 31       |

|    |                                               | 3.3.1          | Compiler-Enforced Cooperative Scheduling                            | 31       |

|    |                                               | 3.3.2          | Eliminating Cache Coherence Stalls in Worker Threads                | 35       |

|    |                                               | 3.3.3          | A Work-Conserving Dispatcher                                        | 36       |

|    | 3.4                                           | Conco          | ord Prototype                                                       | 38       |

|    |                                               | 3.4.1          | API                                                                 | 38       |

|    |                                               | 3.4.2          | Concord Runtime                                                     | 38       |

|    |                                               | 3.4.3          | Concord Compiler                                                    | 38       |

|    | 3.5                                           | Evalua         | ation                                                               | 39       |

|    |                                               | 3.5.1          | Methodology                                                         | 39       |

|    |                                               | 3.5.2          | Evaluating Concord Using Synthetic Microbenchmarks                  | 40       |

|    |                                               | 3.5.3          | Evaluating Concord Using Google's LevelDB                           | 42       |

|    |                                               | 3.5.4          | Evaluating Concord's Mechanisms Individually                        | 44       |

|    |                                               | 3.5.5          | Conclusions Drawn                                                   | 48       |

|    | 3.6                                           | Discus         | ssion                                                               | 48       |

|    | 3.7                                           | Relate         | d Work                                                              | 49       |

|    | 3.8                                           | Key Ta         | akeways                                                             | 50       |

|    |                                               |                |                                                                     |          |

| II | I La                                          | atency         | Interfaces for Systems Code                                         | 51       |

| 4  | Late                                          | ncy Int        | terfaces as Simple, Executable Programs                             | 53       |

|    | 4.1                                           | •              | n Goals and Target Audience                                         | 53       |

|    | 4.2                                           | •              | tion                                                                | 54       |

|    | 4.3                                           |                | ole                                                                 | 55       |

|    | 4.4                                           | Design         | n rationale                                                         | 56       |

|    | 4.5                                           |                | g It All Together                                                   | 58       |

| _  |                                               |                |                                                                     |          |

| 5  |                                               |                | omatically Extracting Latency Interfaces for Software Network Func- |          |

|    | tions                                         |                |                                                                     | 59       |

|    | 5.1                                           | -              | Network Functions?                                                  | 59       |

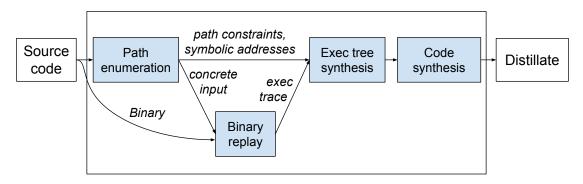

|    | 5.2                                           |                | Overview                                                            | 61       |

|    |                                               | 5.2.1          | Limitations and Assumptions                                         | 61       |

|    | <i>5</i> 2                                    | 5.2.2          | Running Example                                                     | 62       |

|    | 5.3                                           |                | eting General Case Latency Interfaces                               | 63       |

|    |                                               | 5.3.1          | Pre-Analysis of Data Structures                                     | 63       |

|    |                                               | 5.3.2          | Exhaustive Symbolic Execution (ESE)                                 | 64       |

|    |                                               | 5.3.3<br>5.3.4 | Hardware Model for NFs                                              | 65<br>66 |

|    |                                               |                |                                                                     |          |

| Bil | bliogr     | aphy    |                                                                    | 111        |

|-----|------------|---------|--------------------------------------------------------------------|------------|

| 8   | Con        | clusion |                                                                    | 109        |

|     |            | 7.0.1   | Latency Verification Tools That Cut across the Stack               | 107        |

| 7   | Futu       | re Wor  | k Performance Interfaces for Hardware Accelerators                 | <b>107</b> |

| IV  | W          | rappin  | g Up                                                               | 105        |

|     | 6.6        | Conciu  | nsion                                                              | 104        |

|     | 6.5        |         | d Work                                                             | 103        |

|     | 65         |         | Reasoning About Third-party Code                                   | 100        |

|     |            | 6.4.2   | Debugging with Projectors                                          | 97         |

|     |            | 6.4.1   | Distillation Accuracy and Time                                     | 97         |

|     | 6.4        |         | tion                                                               | 96         |

|     | <i>.</i> . | 6.3.3   | Limitations and Assumptions                                        | 95         |

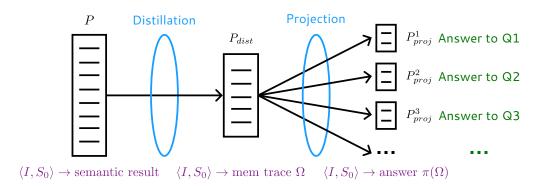

|     |            | 6.3.2   | Projecting the $P_{dist}$ IR into $P_{proj}$ Answers               | 92         |

|     |            | 6.3.1   | Distilling $P$ into the $P_{dist}$ representation                  | 90         |

|     | 6.3        | CFAR    | Design                                                             | 89         |

|     |            | 6.2.2   | Phase 2: Projection                                                | 89         |

|     |            | 6.2.1   | Phase 1: Distillation                                              | 88         |

|     | 6.2        | The CF  | FAR Approach                                                       | 86         |

|     |            | 6.1.3   | An Interface for Cache Usage?                                      | 85         |

|     |            | 6.1.2   | Existing Tools Are Insufficient                                    | 85         |

|     |            | 6.1.1   | Example                                                            | 84         |

|     | 6.1        | Motiva  | ntion                                                              | 84         |

|     |            |         | PU Cache                                                           | 83         |

| 6   | Fror       | n Laten | cy to Side-Effects: Automatically Reasoning About How Systems Code | e          |

|     | 5.9        | Conclu  | asion                                                              | 82         |

|     | 5.8        |         | d Work                                                             | 81         |

|     | 5.7        | •       | arison to Freud                                                    | 80         |

|     | 5.6        |         | JNX Generalize Beyond NFs?                                         | 79         |

|     |            | 5.5.5   | Are Latency Interfaces Useful to NF Operators?                     | 77         |

|     |            | 5.5.4   | Are Interfaces Useful to NF Developers?                            | 75         |

|     |            | 5.5.3   | How Long Does LINX Take to Extract Latency Interfaces?             | 74         |

|     |            | 5.5.2   | Do LINX-Extracted Interfaces Predict Latency Accurately?           | 71         |

|     |            | 5.5.1   | Are LINX-Extracted Interfaces Easy to Read?                        | 69         |

|     | 5.5        |         | tion                                                               | 68         |

|     | 5.4        |         | ting Deployment-Specific Latency Interfaces                        | 67         |

|     |            | 5.3.5   | Resolution-Based Merging                                           | 66         |

# **List of Figures**

| 1.1        | tion Time. SLOs refer to Service Level Objectives                                                                                                                       | 5  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

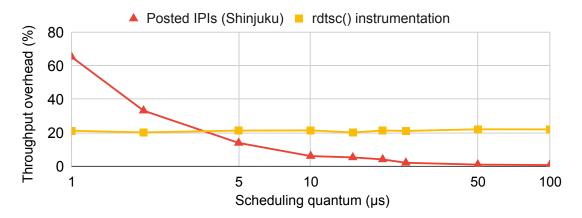

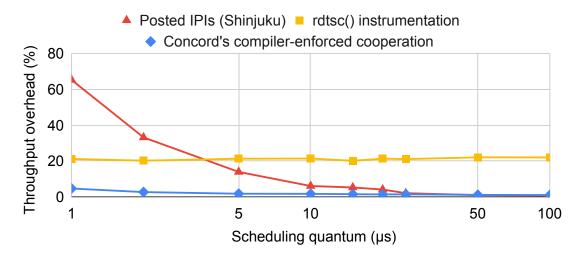

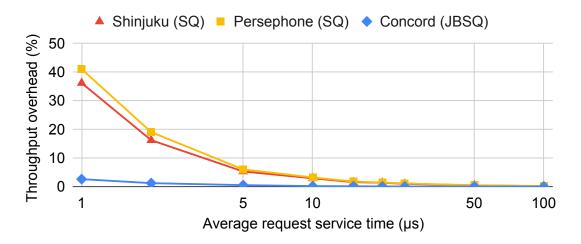

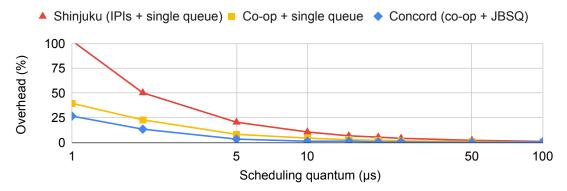

| 3.1<br>3.2 | Abstract visualization of throughput overhead in state-of-the-art datacenter systems.  Overhead of state-of-the-art preemption mechanisms as a function of the schedul- | 26 |

| 3.2        | ing quantum. This overhead excludes the time required to context switch and                                                                                             |    |

| 2.2        | receive a new request.                                                                                                                                                  | 29 |

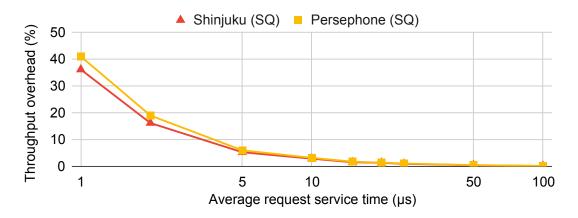

| 3.3        | Time spent idle by a worker thread awaiting the next request in state-of-the-art Single Queue (SQ) systems                                                              | 30 |

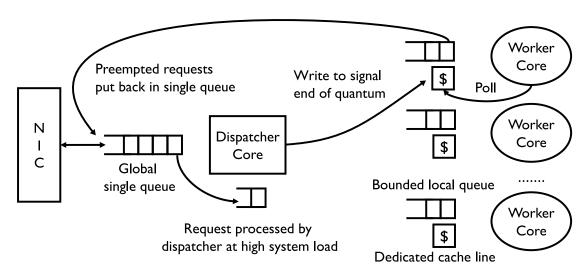

| 3.4        | The Concord architecture. Compiler-enforced cooperation relies on communicating via a shared cache line, $JBSQ(k)$ employs bounded core-local queues to                 | 3( |

|            | eliminate coherence stalls, and the dispatcher's steals work at high load                                                                                               | 32 |

| 3.5        | Comparing the throughput overhead introduced by Concord's compiler-enforced cooperation to that of state-of-the-art preemption mechanisms. This overhead                |    |

|            | excludes the time required to context switch and receive a new request, which is                                                                                        |    |

|            | identical across all systems                                                                                                                                            | 33 |

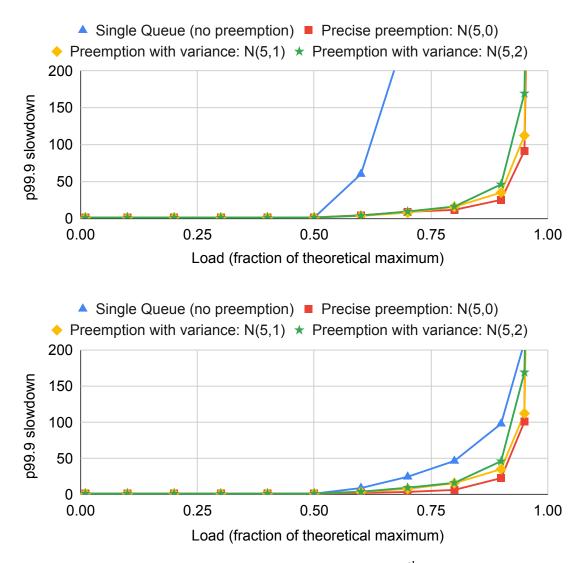

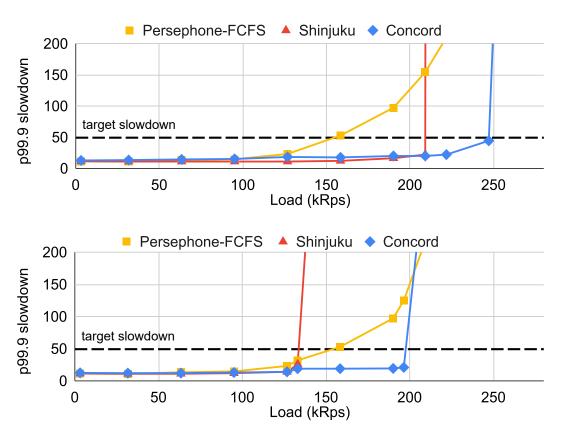

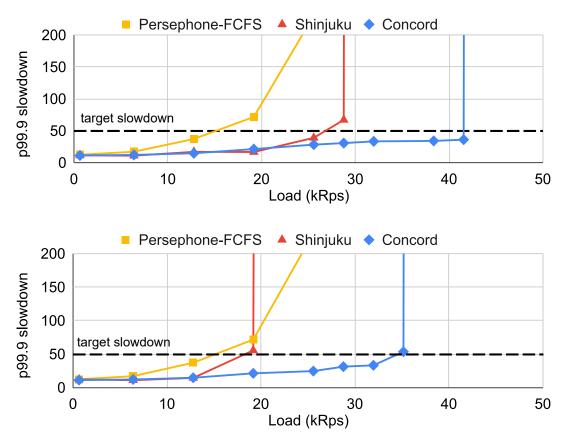

| 3.6        | The impact of non-instantaneous preemption on $99.9^{th}$ percentile request slow-                                                                                      |    |

|            | down for Bimodal(99.5 : 0.5, 0.5 : 500) (top) and Bimodal(50 : 1, 50 : 100) (bottom)                                                                                    |    |

|            | service time distributions. $N(x, y)$ represents a normal variable with mean $x$ and                                                                                    |    |

| 2.7        | standard-deviation <i>y</i>                                                                                                                                             | 35 |

| 3.7        | Time spent idle by a worker thread awaiting the next request in Single Queue                                                                                            | 25 |

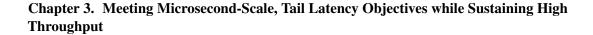

| 3.8        | (SQ) and JBSQ systems                                                                                                                                                   | 37 |

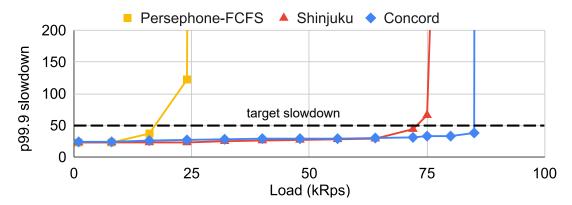

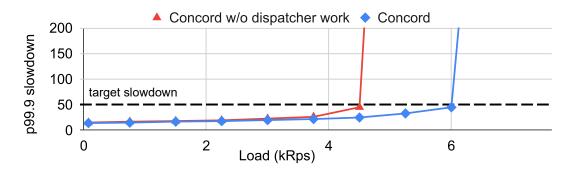

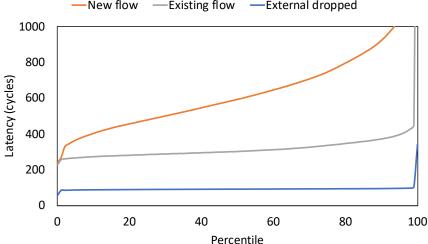

| 3.8        | 99.9 <sup>th</sup> percentile slowdown vs load for Bimodal(50:1,50:100). Scheduling quantum is $5\mu s$ (top) and $2\mu s$ (bottom)                                     | 41 |

| 3.9        | 99.9 <sup>th</sup> percentile slowdown vs load for Bimodal(99.5:0.5,0.5:500). Scheduling                                                                                | 7. |

| 3.7        | quantum is 5µs (top) and 2µs (bottom)                                                                                                                                   | 42 |

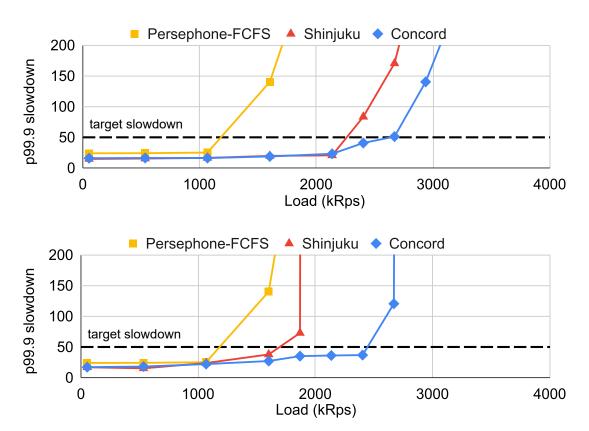

| 3.10       | 99.9 $^{th}$ percentile slowdown vs load for Fixed(1) (top) and TPCC (bottom) service                                                                                   |    |

|            | time distributions.                                                                                                                                                     | 43 |

| 3.11       | 99.9 <sup>th</sup> percentile slowdown vs load for a levelDB server running 50% GETs,                                                                                   |    |

|            | 50% SCANs. Scheduling quantum is 5μs (top) and 2μs (bottom)                                                                                                             | 44 |

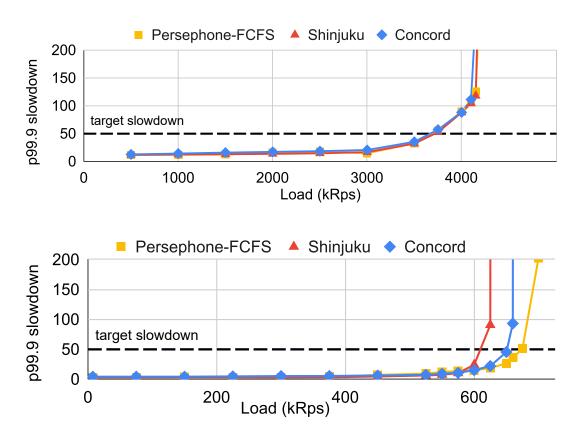

| 3.12       | 99.9 <sup>th</sup> percentile slowdown vs load for a LevelDB server running a workload                                                                                  |    |

|            | based on ZippyDB production traces [37]. Scheduling quantum is 5µs. We do                                                                                               |    |

|            | not use a 2μs quantum since all requests run longer than 2μs                                                                                                            | 45 |

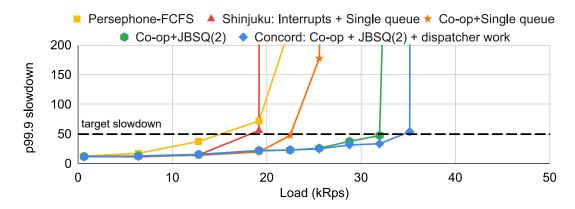

| 3.13       | Contribution of each Concord mechanism towards throughput improvement for                                                                                               |    |

|            | the LevelDB server in Fig. 3.11(b)                                                                                                                                      | 47 |

|            | Preemption overhead across scheduling quanta.                                                                                                                           | 47 |

| 5.15       | Application throughput for dedicated dispatcher vs. Concord dispatcher in a 4-core configuration                                                                        | 47 |

| 4.1        | Example implementation of a MAC learning bridge                                                                                                                         | 55 |

| 4.2        | General case latency interface for MAC learning bridge                                                                                                                  | 56 |

#### **List of Figures**

| 4.3  | Example deployment-specific latency interface for MAC learning bridge                                 | 56  |

|------|-------------------------------------------------------------------------------------------------------|-----|

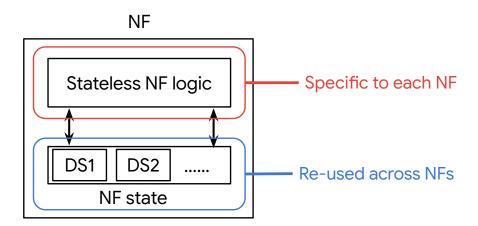

| 5.1  | Typical architecture of NF code. DS refers to data structures that the NF uses to store mutable state | 60  |

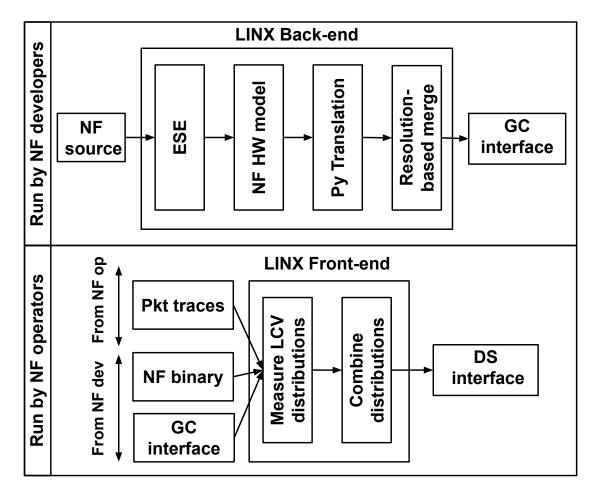

| 5.2  | Overview of LINX. GC and DS refer to general case and deployment-specific                             |     |

|      | respectively. ESE refers to Exhaustive Symbolic Execution                                             | 62  |

| 5.3  | Latency interfaces extracted for the lpmGet method from Algorithm 1                                   | 64  |

| 5.4  | Example of LINX's constraint rewriting                                                                | 67  |

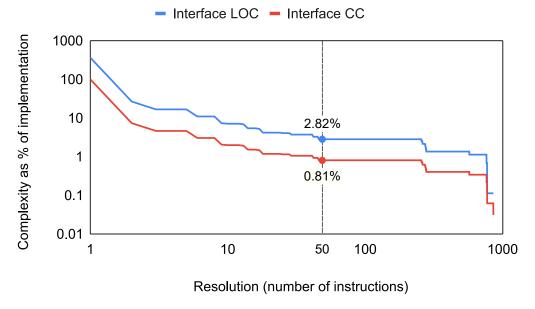

| 5.5  | Impact of varying resolution on the size (LOC) and complexity (CC) of Katran's                        |     |

|      | latency interface. Both axes are in log scale                                                         | 70  |

| 5.6  | Extracted general case interface for VigNAT                                                           | 71  |

| 5.7  | Deployment-specific interfaces for VigNAT (50 <sup>th</sup> and 95 <sup>th</sup> percentile) and the  |     |

|      | latency CDF (resolution=200 cycles)                                                                   | 72  |

| 5.8  | Interface for map_contains() before and after the bug fix. t is the LCV for                           |     |

|      | traversals in the hash ring                                                                           | 76  |

| 5.9  | Interfaces for VigNAT (top) and DPDK NAT (bottom): VigNAT does checksums                              |     |

|      | in software, while DPDK NAT offloads checksums to the NIC as much as possible.                        | 77  |

| 6.1  | Example <i>P</i> on left (Hyperkernel's sys_create system call that creates a new                     |     |

|      | file) and the corresponding $P_{dist}^{data}$ distillate                                              | 87  |

| 6.2  | $P_{dist}^{instr}$ distillate for sys_create                                                          | 87  |

| 6.3  | The CFAR workflow                                                                                     | 88  |

| 6.4  | The four components of CFAR's analysis                                                                | 90  |

| 6.5  | $P_{dist}^{data}$ for memcmp                                                                          | 93  |

| 6.6  | Projection for buggy mmap code showing number of unique cache lines                                   | 98  |

| 6.7  | mmap projection after fix                                                                             | 99  |

| 6.8  | Projection showing how instruction count for AES's cipher unpadding function                          |     |

|      | is a function of buffer.padding_length, which must remain secret                                      | 100 |

| 6.9  | Projection showing instruction count for AES's cipher unpadding function after                        |     |

|      | our fix                                                                                               | 100 |

| 6.10 | Measured latency for TCP packet processing as a function of the number of                             |     |

|      | connections                                                                                           | 101 |

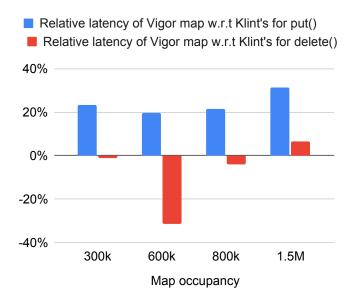

| 6.11 | Relative latency of the Vigor map as compared to Klint's for put () and delete()                      |     |

|      | calls. Positive (negative) numbers indicate that the Vigor map is slower (faster).                    | 102 |

# **List of Tables**

| 2.1 | Comparison of the precision and completeness of existing approaches to representing system latency. System state refers to the state maintained by the system implementation in software. Performance annotations are partially complete with respect to system state since they can take into account state maintained as explicit, global variables. | 16 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 |                                                                                                                                                                                                                                                                                                                                                        | 1  |

| 3.1 | Overhead and timeliness of Concord's instrumentation compared to Compiler-<br>Interrupts (CI) [22]. The baseline (0% overhead) corresponds to un-instrumented                                                                                                                                                                                          |    |

|     | code. Concord's overhead is often negative due to its loop unrolling                                                                                                                                                                                                                                                                                   | 46 |

| 4.1 | General-case performance of procedures called by the code in Fig. 4.1                                                                                                                                                                                                                                                                                  | 55 |

| 5.1 | Network functions used to evaluate LINX                                                                                                                                                                                                                                                                                                                | 69 |

| 5.2 | Complexity of extracted interfaces vs NF implementation. " $(x\%)$ " means " $x\%$ of                                                                                                                                                                                                                                                                  |    |

|     | implementation". For each NF, the complexity is calculated for an interface with                                                                                                                                                                                                                                                                       |    |

|     | resolution equal to 10% of the maximum latency variability the NF can exhibit.                                                                                                                                                                                                                                                                         | 70 |

| 5.3 | LINX's average (maximum) prediction error for hardware-independent metrics                                                                                                                                                                                                                                                                             |    |

|     | for typical (Typ) and adversarial (Adv) traffic                                                                                                                                                                                                                                                                                                        | 73 |

| 5.4 | LINX's average (maximum) prediction error for CPU typical in comparison to a                                                                                                                                                                                                                                                                           |    |

|     | WCET-based model for typical (Typ) and adversarial (Adv) traffic                                                                                                                                                                                                                                                                                       | 74 |

| 5.5 | Time taken by LINX to extract the general case interfaces                                                                                                                                                                                                                                                                                              | 74 |

| 5.6 | Latency regressions in Katran (handling new flows)                                                                                                                                                                                                                                                                                                     | 75 |

| 5.7 | Throughput and latency of three NFs using map, shown before/after each perfor-                                                                                                                                                                                                                                                                         |    |

|     | mance bug fix                                                                                                                                                                                                                                                                                                                                          | 76 |

| 5.8 | Performance bugs used for root-cause diagnosis                                                                                                                                                                                                                                                                                                         | 78 |

| 5.9 | Summary of our experiments with Freud                                                                                                                                                                                                                                                                                                                  | 81 |

| 6.1 | Time taken by CFAR to extract distillates                                                                                                                                                                                                                                                                                                              | 97 |

| 6.2 | OpenSSL programs analyzed using CFAR's $\mathscr{P}_{crypt}$                                                                                                                                                                                                                                                                                           | 99 |

# Setting the stage Part I

## 1 Introduction

Large and complex computer systems such as those that power Google's web search, Amazon's e-commerce, or Netflix's video streaming are an integral part of everyday life for billions of people. More than 5.1 billion people [174] (65% of the global population) are active internet users which results in more than 3.5 billion Google search queries being made [173], 15 million e-commerce packages being shipped [171], 1 billion hours of video streaming content being watched [244], and 350 billion emails being exchanged on a daily basis [172].

To build such complex systems *correctly*, i.e., ensure that they provide the desired functionality, developers need *semantic interfaces* such as header files, documentation, and/or specifications. Such complex systems typically consist of numerous components, each of which is built by a different team of developers. Since semantic interfaces provide succinct, human-readable descriptions of the functionality that a piece of code or system component provides, developers can quickly use, build upon, and deploy code that was written by others while being confident that the system as a whole correctly implements the desired functionality.

However, given how integral such systems are to everyday life, it is no longer sufficient for them to be correct; they are also expected to be *interactive*, i.e., deliver consistently low latencies to provide a seamless user experience. Failure to provide consistently low latencies can directly impact revenue: for example, Amazon is known to lose 1% of sales for every additional 100*ms* in latency [235], while a 500*ms* delay in Google's search results causes a 20% drop in traffic and thus advertisement revenue [221]. Similarly, brokers can lose up to \$4 million per millisecond if their platform is 5*ms* behind the competition [235] and a 2017 Akamai study showed that a 100*ms* delay results in a 7% decrease in the number of customers that complete transactions [4].

There exists no equivalent *latency interface* that developers can use to reason precisely about the expected latency behavior of code. Engineers today reason about latency in terms of envelopes (e.g., "runs in O(n) time") and benchmarks, which implies that they deploy their system without understanding the entire spectrum of latency it can exhibit. As a result, systems frequently exhibit unexpected performance behavior [80, 100, 105] in production when the input workload or runtime environment changes in unpredicted ways which results in missed performance targets and a perpetual need to fix performance bugs [98, 127]. To give a sense of how much work this is, half the configuration-related patches in open-source cloud systems are needed to fix performance issues, while Mozilla developers have had to fix from 5 to 60 performance bugs every month over the past 10 years [127].

So in this thesis, we answer the question(s): Can there exist a useful latency interface for systems code? i.e., an interface that summarizes the latency behavior of systems code, just like a semantic interface summarizes its functionality? What should such an interface look like to help developers reason precisely about the expected latency of not just their own, but also third-party code?

#### 1.1 Reasoning about System Latency Today

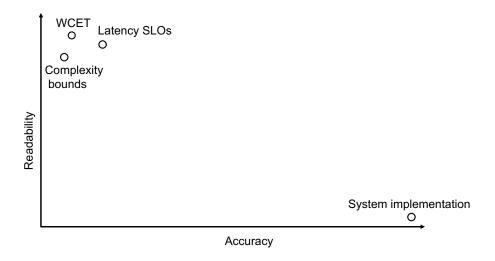

To help developers reason about expected latency behavior, latency interfaces need to provide a balance between two, typically conflicting properties: *accuracy* and *readability* [144]. By accuracy, we mean the ability to describe latency *completely* (for every possible input and runtime environment) and *precisely* (with a small error). By readability, we mean that the representation should be *smaller* than the system implementation and as *abstract* as possible, i.e., summarize latency in terms of primitives appropriate for a semantic interface of the system, and reveal implementation details only when necessary. Accuracy and readability are conflicting requirements because improving accuracy typically involves adding more detail, which makes the representation harder to read.

Widely-used representations such as asymptotic complexity bounds [25], upper bounds on worst-case on execution time [237] and probabilistic service level objectives (SLOs) [208] typically sacrifice accuracy for readability, i.e., there are many inputs for which they do not accurately describe latency.

Asymptotic bounds on time complexity (e.g., "runs in O(n) time") [25] describe the limiting behavior of the number of computational steps the program must perform as a function of the size of its input (n). While such bounds are easy to read (and hence widely used), they cannot provide developers with a precise understanding of latency in terms of wall clock time. This is because they ignore both the constants in the latency expression and factors such as the underlying hardware. Constants and hardware often end up being the dominant factor in wall clock time; for instance, it is common to trade off algorithmic complexity for improved locality (and thus lower constants) in memory and storage devices [69, 70, 238].

Upper bounds on worst-case execution time (WCET) [237] are widely used in the domain of real-time and safety-critical systems (e.g., control systems in airplanes [213, 232], cars [230] and industrial manufacturing [231]) where the timeliness of executing an operation is part of its semantic correctness. While such bounds are both easy to read and expressed in terms of wall-clock time, they are not very useful beyond real-time and safety-critical systems. This is because most systems are designed to be fast in the common case and make progress in the worst [144], and so worst-case latencies may be orders of magnitude higher than typical or median latencies and cannot be used to make informed development decisions.

Finally, latency SLOs [208] provide a target value or range for the statistical execution latency of the system (e.g., X percentage of requests take < Y time). In theory, SLOs overcome the primary limitations of both of the above representations since they reason about wall clock time and can be used to describe latency in scenarios other than the worst case. However, in practice, SLOs typically deteriorate to worst-case upper bounds. For instance, a recent paper from Google states that "SLOs are aimed at bad outcomes, they are often far from the expected outcomes, and few customers would be happy if a system only met its contractual SLOs" and calls for SLOs to take the expected workload into account [162].

In the absence of a readable and accurate representation, most developers resort to benchmarking a system in order to reason about its latency behavior, i.e., they treat the system implementation as its own interface. Benchmarking is not only a tedious process but is also error-prone, particularly when used to understand the latency behavior of code that the developer did not write themselves [112].

Fig. 1.1 summarizes the quandary that developers face when trying to reason about the expected latency behavior of systems code. They must either divine the expected latency behavior of systems code from representations that provide little information about latency for realistic workloads or download, build, write tests for, and run the code themselves to discover the expected latency. In contrast, they can reason about expected functionality just by reading the succinct semantic interface.

Figure 1.1: Existing representations of system latency. WCET refers to Worst-Case Execution Time. SLOs refer to Service Level Objectives.

#### 1.2 Thesis Goals

The goal of this thesis is to develop representations and techniques that enable developers to reason about the expected latency behavior of systems code as easily as they reason about its expected functionality today.

By systems code, we refer to the software that bridges applications to the hardware and infrastructure that executes it. Systems code typically performs low-level operations (e.g., DMA), and the quintessential examples of systems code are operating systems, hypervisors, device drivers, and variants thereof (such as network functions running on kernel-bypass frameworks). Systems code plays a foundational role in the software stack; as a result, upper layers rely on it being optimized for speed and efficient resource usage. Languages traditionally associated with systems programming are C, C++, and Rust, languages that provide facilities for low-level

#### **Chapter 1. Introduction**

memory manipulation and hardware access, while also allowing for higher-level abstractions when needed.

We advocate that achieving our goal requires systems code to have a latency interface that describes its expected latency behavior and related side effects in an accurate and readable manner, just like the code's semantic interface describes its expected functionality and related side effects.

We take a three-part approach to realize latency interfaces for systems code.

In the first part of the thesis (§1.2.1), we show how to design operating system schedulers that enable datacenter applications (such as the ones underlying web search and e-commerce) to provide predictable latency behavior, i.e., latency that conforms to a well-defined interface and is hence easy to reason about. Here, we work with existing representations of latency, and so define the latency interface using tail latency SLOs, which is the standard practice in datacenters today. We contribute Concord, an efficient scheduling runtime for datacenter applications that carefully eliminates sources of overhead that plague state-of-the-art schedulers and lead to worse tail latency. While Concord achieves its goals, our experiences in this part of the thesis motivated us to develop interfaces and techniques that provide a more precise understanding of latency behavior and related micro-architectural effects.

In the second part of the thesis (§1.2.2), we propose a new representation for latency interfaces—simple, executable programs that accepts the same input(s) as the system and output its processing latency—that we believe is best suited to describing the expected latency behavior of systems code in an accurate and readable manner. We concretize this representation in the domain of network functions (NFs) and present LINX, a program analysis tool that automatically extracts latency interfaces from NF implementations.

Finally, since an interface should describe related side effects [207], we present CFAR, a technique and tool that allows developers to reason precisely about micro-architectural side effects (specifically CPU cache usage) of systems code (§1.2.3). Our work on CFAR demonstrates that simple, executable programs can summarize not only the processing latency but also any related side effects of systems code in an accurate yet readable form.

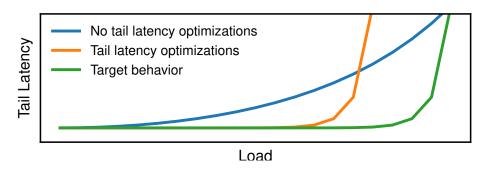

#### 1.2.1 Ensuring that Datacenter Applications Meet Their Latency Objectives

Datacenter applications are expected to meet strict microsecond-scale tail latency SLOs (e.g.,  $99^{th}$  percentile latency should be  $< X\mu s$ ) to remain interactive for end users [131, 182, 190]. Bounding tail latency (typically  $99^{th}$  percentile or higher) is necessary because of the "tail-at-scale" problem [62]: given that such applications distribute each user request across thousands of servers with the end-to-end response time determined by the slowest individual response, it becomes highly likely that at least one server will incur a high percentile latency that will end up determining the end-to-end response time. Additionally, for the application as a whole to remain interactive and respond to user requests within tens of milliseconds, each individual server should

process requests within ten to a few hundred microseconds [21, 131, 190].

We focus on ensuring that such applications meet their tail latency SLOs in a cost-effective manner, i.e., while sustaining high throughput per server. Taking cost into account is necessary since the easiest way to ensure that tail latency SLOs are met is to overprovision the number of servers required and have each server serve a smaller fraction of the incoming load [63, 151]. However, this overprovisioning wastes precious CPU cycles and is not economical for services that need to scale to billions of users [62, 131].

Since tail latency is dominated by queueing delay (not service time), we advocate for rethinking microsecond-scale scheduling and present Concord, an efficient scheduling runtime for microsecond-scale datacenter applications. Concord demonstrates that careful *approximation* (as opposed to canonical implementation) of theoretically optimal scheduling policies enables new microsecond-scale mechanisms that provide significant throughput benefits while ensuring the applications continue to meet the same tail latency SLO. Concord introduces new mechanisms that carefully approximate two scheduling policies to reduce their implementation overhead and thus improve application throughput: (1) Preemptive scheduling, which is necessary to prevent long-running requests from starving short-running ones but introduces the overhead of having to context-switch between requests, and (2) Single-queue scheduling, which is necessary to ensure optimal load balancing of incoming requests but introduces cache coherence overheads due to requests being passed from the CPU core maintaining the single queue to the one that processes the request.

Designing and implementing Concord made us acutely aware of the two main challenges that system developers face when trying to reason about the latency behavior of systems code. First, reasoning precisely about the differing latency behavior of different execution paths through the code (e.g., processing of different request types) is hard; a direct consequence of this is that developers are forced to rely on high-overhead, black box techniques such as interrupts to preempt long-running requests. Second, developers possess little visibility into the micro-architectural (specifically CPU cache) behavior of their code. As a result, cache issues (such as the ones associated with single queue scheduling) often go unaddressed even in state-of-the-art systems focused on maximizing performance [63, 131].

While it is feasible to overcome these challenges (as we did) using the traditional systems approach—carefully measure, analyze, optimize, repeat—it is a painstaking process that needs to be repeated for every system. Hence, in the next two parts of the thesis, we focussed on developing interfaces and techniques that provide a more precise understanding of latency behavior and related micro-architectural effects.

#### 1.2.2 An Accurate, Readable Representation for System Latency

Here, our goal is to answer the question: *Is it feasible to summarize the processing latency of systems code for all possible inputs in an interface that is simultaneously accurate and readable?*<sup>1</sup>

Summarizing processing latency in an accurate yet readable interface is more challenging than doing the same for semantics because the system's deployment environment (e.g., the hardware it runs on) typically has a greater impact on its latency than on its semantics. This is because systems—both hardware and software—typically employ strong semantic modularity but close to no latency modularity. For instance, a mov (%ebx), %eax instruction has the same semantics on all x86 machines but when it comes to latency, the modularity is much weaker: the time to execute mov (%ebx), %eax can vary by orders of magnitude depending on several factors such as the micro-architectural specifics of the machine and other processes executing on the same machine.

We propose that the *latency interface* of a system be a *program* that accepts the same inputs as the system and outputs how long the system would take to process the given input. System developers are intuitively familiar with code, allowing them to quickly read such interfaces and understand the latency behavior of the system without having to run it. Accepting the same input(s) enables the interface to describe performance for different expected workloads, something that upper/lower bounds cannot do.

We introduce three key ideas that enable latency interfaces to summarize latency in a manner that is simultaneously accurate and readable: First, the interfaces describe latency not as concrete numbers but as formulae of random variables that we call *latency-critical variables (LCVs)*. LCVs summarize the impact of latency of all factors other than the current input (e.g., prior inputs, system state, configuration, and runtime environment) on latency. Representing latency as formulae containing LCVs enables the interface to succinctly summarize the latency for arbitrary workloads. Second, we introduce the concept of a latency resolution which specifies the smallest change in latency that the interface captures. At a given resolution the interface only reveals those implementation details that cause latency variability greater than the resolution, thus eliminating unnecessary details and giving developers who do not care about cycle-accurate latency predictions (whom we expect to be the majority) explicit control over the trade-off between accuracy and readability. Finally, we introduce the concept of deployment-specific interfaces, i.e., interfaces tailored to a particular deployment. Deployment-specific interfaces enable developers who merely want to use the system in a particular deployment environment to maximize readability while retaining all information relevant to latency behavior in that environment.

We concretize our proposal for latency interfaces in the context of software network functions (NFs)—in-network packet processing applications such as load balancers, firewalls, and NATs—and present LINX, a tool that automatically extracts latency interfaces from NF implementa-

<sup>&</sup>lt;sup>1</sup>We focus on systems code that provably terminates to avoid running into the Halting problem [220]

tions. LINX takes as input NF code written in C and outputs latency interfaces in the form of simple Python programs. Under the covers, LINX relies on automated program analysis, binary instrumentation, and NF-specific, empirical hardware models to extract accurate yet readable interfaces.

#### 1.2.3 Reasoning About Latency Side Effects

Since a program's semantic interface describes not only its expected output(s) but also any expected side effects [207], i.e., modifications to shared state that may lead to differences in externally observed behavior, an equivalent latency interface should also describe any expected latency side effects in addition to the processing latency described above.

Latency side effects arise due to shared micro-architectural state. Since all programs running on the same CPU core (e.g., caller and callee, application and operating system) share core-local micro-architectural resources (e.g., data and instruction caches, TLB, branch predictor, etc.) calling into a piece of code has not only a direct impact on latency (via the execution latency of callee) but also an indirect cost that depends on how the callee perturbs shared micro-architectural state. This indirect cost is a frequently observed source of latency variability; for example, FlexSC [212] showed how a system call can take up to  $3 \times$  longer depending on the invoking program's micro-architectural resource usage, while the invoking program may run up to  $4 \times$  slower after the system call, depending on the system call's micro-architectural resource usage.

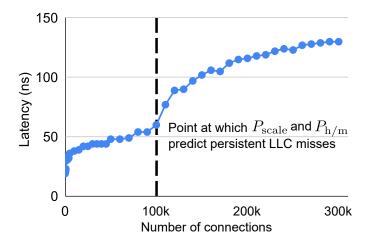

We focus on a dominant source of micro-architectural side effects, namely the CPU cache. Our goal is to enable developers to answer frequently asked questions about how a piece of systems code interacts with the cache, such as: How does the code's cache usage vary with workload (e.g., as a function of the number of network connections)? Which workloads make the working set exceed the cache size? Existing performance-analysis tools such as profilers [32, 150, 186, 226] cannot directly answer the questions listed above, because they do not understand what the code does to the micro-architecture as a function of workload.

We present CFAR (Cache Footprint AnalyzeR), a tool that processes a piece P of systems code into answers to developers' questions about how that code uses the cache. CFAR's processing consists of two phases: In the former, CFAR takes as input the code and outputs an intermediate representation (a "distillate") that contains all the information on how the code accesses memory. In the latter, developers can write simple programs ("projectors") that use the distillate to compute answers ("projections") to specific questions about P's cache usage.